随着台积电2nm即将在今年年底量产,2026年下半年则将正式跨入埃米时代,芯片微缩即将达到物理极限,原子层沉积(Atomic Layer Deposition,简称“ALD”)将成为延续摩尔定律、半导体微缩的关键技术之一。 对此,台媒Technews专访荷兰半导体制造设备大厂ASM国际(又称“ASMI”)技术副总裁Glen Wilk,介绍了ALD在制程微缩方面的重要性。

ALD何那么重要? 跟 CVD、PVD 差异在哪?

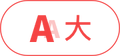

ALD 主要特性之一是逐层沉积原子,是可以将材料一层一层成长的薄膜制程技术,“你可以想像成下雪,每当只落下一层雪花时,可使沉积非常均匀且拥有良好的覆盖性”,Wilk 表示,ALD 技术能使沉积沿着边缘沉积,甚至在底部、侧面或上方都能逐层沉积。

相比之下,PVD(物理气相沉积)则是“直线沉积”,如同箭一样只能沿着射向(直线路径)飞,因此无法转弯或在底部、角落沉积,因此PVD的覆盖能力非常有限,只能往一个方向沉积。

至于CVD(化学气相沉积)与ALD较为相似,但每次沉积不是单层原子,而是多层原子,虽然具有一定的覆盖能力、可沉积到凹角,但不如ALD精准。 Wilk 指出,尤其是特地部分(如底部、角落)进行精确控制时,CVD 就做不到,虽然速度较快,但精准度不如 ALD。

▲ PVD、CVD、ALD 三种沉积方式示意图

当制程走向2纳米以下,ALD技术面临三大挑战

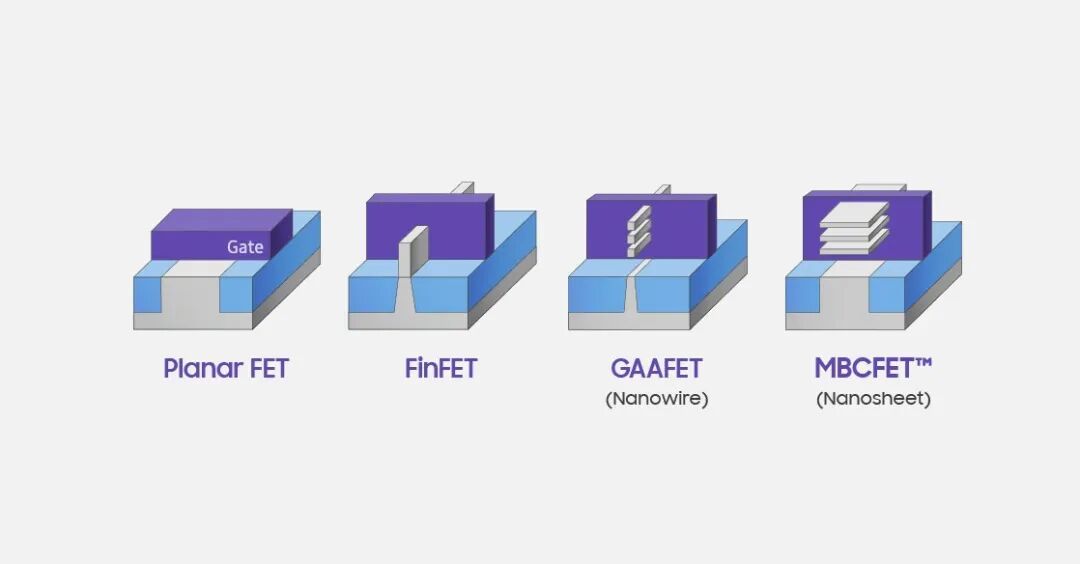

随着GAA、3D架构发展,由于深宽比更高、沟槽更深窄,对于沉积覆盖性、精准度与厚度控制要求更高。 Wilk 表示,有些结构会有两片不同片层,需要顶部和底部都进行沉积,当两边可能在中间相遇时,要避免发生“堵塞”(clogging)状况。 以吸管为例,若在吸管内侧涂色,很容易卡在前方或入口处,加上内部又细又窄,材料可能堆积上方,难以深入底部,因此涂得均匀且厚薄度控制得当,变得更困难。

第二个挑战是“区域选择性沉积”(Area Selective Deposition,简称 ASD)。 传统进行ALD技术时,会精确且覆盖所有地方,但现在需求转向在芯片特定区域沉积,因此“选择性沉积”和“局部沉积”成为重要技术,能节省后续曝光和加工步骤,从而降低成本。

第三个挑战是“填缝”(Gap Fill)。 若在结构之间填充时,传统方式会让两侧材料在中间相遇并形成一条缝隙(Seam),当后续再经历蚀刻或其他制程,缝隙恐越撑越大,最终导致裂开。 解决办法是通过“无缝隙填充”(Seam-free gap fill)的方式,直接完整填满中间结构,避免两侧材料碰在一起产生缝隙。

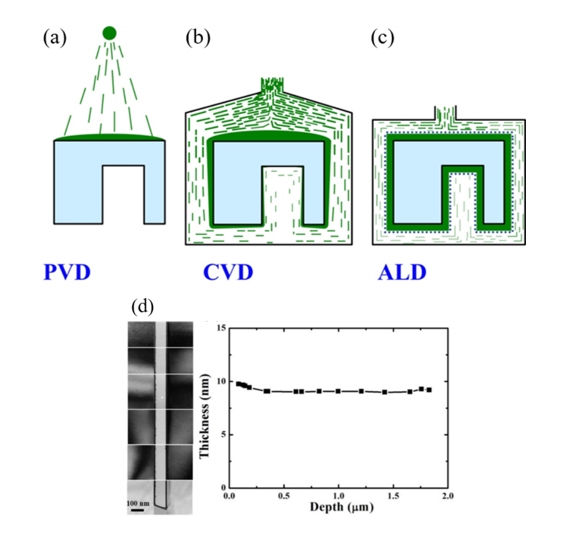

▲ CFET 为图右的架构,三星称为 MBCFET

这些都是制程微缩下遇到的挑战,Wilk表示,ASM已率先开发选择性沉积(ASD)技术,帮助客户有效解决先进制程挑战,提升制程良率、组件可靠性与整体效能。

他也指出,若进一步走到CFET架构,ALD沉积将面临更多挑战,主要在“低温沉积”和“选择性沉积”,要求将比 GAA 更严格。 GAA 挑战是一层堆叠,而 CFET 是在这上面再堆叠一层(即堆叠两层以上),如同盖高楼一样,如何从上到下实现超薄且均匀的沉积,且不能产生缝隙,是个棘手问题。

此外,CFET对低温沉积要求更高。 过去GAAFET架构是一次同时完成制程,所以对高温处理没问题; 但到CFET架构,可能面临需先制造上面两层、再进行下面两层,而制作新结构时需要高温,使得已完成的旧结构需面临二次高温,恐导致损坏或性能退化。 此外,低温沉积又会面临元素(如碳)残留问题,亦是挑战之一。

▲ 从上图可知,CFET 架构的沟槽更得深窄,沉积也变得棘手。 (Source:台积电)

化学材料+硬件双引擎! ASM靠研发团队维持ALD技术领先

针对这些挑战,ASM决定从材料和硬件设备下手找寻新解方。 该公司旗下的企业研发部(Corporate R&D,简称CRD)负责开发先进化学与制程解决方案。 一部分团队位于芬兰,与赫尔辛基大学合作,主要着重在材料开发、前驱物筛选以及新路径探索; 另一团队与半导体研发中心 imec 合作,进一步验证和模拟真实环境测试。

这些团队专注于研究新的化学反应与新分子,以克服目前特定区域沉积、堵塞问题。 Wilk 强调,这需要大量全新的化学配方与创新,这也是 ASM 独有的优势。 此外,作为ALD领先设备供应商,ASM也在改善硬件设计,使其与新化学配方、新分子与新解决方案相匹配,并有效输送化学物质,使其能在晶圆上达到均匀覆盖,同时保持高效率与高速度。

“ASM 早在 1999 年收购芬兰公司 Microchemistry,而 ALD 技术正是由这间公司发明,ASM 也传承了这项专业能力。”Wilk 认为,化学专业是 ASM 优势之一,能根据这些化学特性去设计对应的硬件设备是另一大优势,“通过化学与硬件的结合,正是我们一直保持领先、并视为核心差异化的关键所在”。

全面布局新材料研发,ASM瞄准无缝隙填充、低温沉积与选择性沉积

ASM 研究重点包括各类型填隙材料(二氧化硅、氮化硅)、新型闸极堆叠材料(功函数金属与偶极)、高导热绝缘层、新型接触材料、低温磊晶、硅/硅锗 3D DRAM 磊晶堆叠等,也针对各种薄膜进行研究,解决客户在上述制程中遇到的问题。

此外,ASM旗下也有负责规划先进技术的前瞻部门,与客户密切合作,探索潜在解决方案。 目前公司正着手开发新材料,例如能快速导热、有效散热的材料,以及开发在极薄条件下依然运作良好(如良好绝缘或导电)的新材料,以取代传统较厚的膜层,另在化学前驱物也有诸多合作。

通过CRD早期合作,ASM能及早了解客户需求并测试解决方案,可在真实环境中不断测试与学习,提高成功率,提前向客户推广开发的新材料层,这是ASM独有的横向/企业级的研发,也是公司的差异化优势。

Wilk 表示,不管是“无缝隙填充”、“低温沉积”或者“选择性沉积”,都是目前竞争最激烈的领域。 ASM 已持续进行化学材料的开发,搭配专门与之相匹配的硬件设计,且可简化制程步骤、大幅提升产能,进一步为客户节省成本。

除了ALD外,磊晶也成为GAA时代下一大难题

在摩尔定律持续推进制程微缩,FinFET时代晶体管通道的厚度主要由微影与蚀刻决定; 随着技术演进至GAA架构,硅通道则改由具备原子级精准度的磊晶制程直接生长而成。

Wilk 表示,当来到 GAA 时代,磊晶会面临“低温”与“生长纳米片(Nanosheet)”两大挑战,前者因背面供电技术,使温度控制更困难,加上低温环境容易引入杂质,导致品质下滑,成关键挑战之一; 后者在建构通道制程时,必须交替生长磊晶,制作出间距分开的多个硅通道,这又涉及到界面锐利度(Interface Sharpness)问题。

对此,ASM也将技术延伸至磊晶领域,强调公司磊晶设备的硬件设计与竞争对手不同,能在低温下实现更好控制,同时沉积出非常均匀且高质量的薄膜。 在先进封装的“混合键合”(Hybrid Bonding)部分,ASM可提供混合键合层及相关表面处理技术,另在晶粒堆叠整合过程中,须通过高导热性的绝缘层来散热,也成为ASM另一大机会。

“台湾团队对 ASM 来说非常重要!”ASM指出,台湾做为全球半导体产业的核心枢纽,一直都是公司业务发展策略中最不可或缺的一部分,去年启用新竹办公室将聚焦研发与客户支持,而台南也设有培训中心,负责支持本地需求及培育其他国家工程师的培训中心; 至于全球布局部分,ASM目前主要制造基地位于新加坡、第二制造中心位于韩国,现有产能相当充足。 为了因应目前政经状况,ASM也将于2027年在美国新增研发单位据点,做为新工具测试地点。